# USN

## Third Semester B.E. Degree Examination, December 2011

## **Analog Electronic Circuits**

Time: 3 hrs.

Max. Marks:100

Note: 1. Answer any FIVE full questions, selecting at least TWO questions from each part.

2. Missing data, if any, may be suitably assumed.

#### PART - A

- 1 a. Explain the following with respect to a semiconductor diode:

- i) Diffusion capacitance

- ii) Transition capacitance and

- iii) Reverse recovery time.

(06 Marks)

- b. Explain the working of a half wave rectifier. Also determine ripple factor, efficiency and peak inverse voltage. (08 Marks)

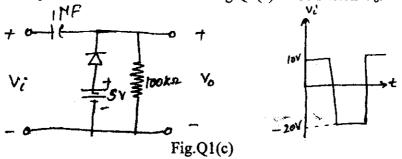

- c. Determine V<sub>0</sub> for the network shown in Fig.Q1(c). Also sketch V<sub>0</sub>.

(06 Marks)

- 2 a. In a voltage divider bias circuit of BJT  $R_C = 4K\Omega$ ,  $R_E = 1.5K\Omega$ ,  $R_1 = 39K\Omega$ ,  $R_2 = 3.9K\Omega$ ,  $V_{CC} = 18V$  and  $\beta = 70$ . Find  $I_{CQ}$  and  $V_{CEQ}$ . (08 Marks)

- b. In an emitter bias configuration  $I_{CQ} = \frac{1}{2}I_{CSat}$  and  $I_{CSat} = 8mA$ ,  $V_{CC} = 28V$  and  $V_{C} = 18V$ ,

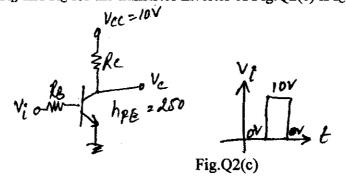

$\beta$  = 110. Determine R<sub>C</sub>, R<sub>E</sub>, R<sub>B</sub> and stability factor S(I<sub>CO</sub>). (06 Marks) c. Determine R<sub>B</sub> and R<sub>C</sub> for the transistor inverter of Fig.Q2(c) if I<sub>CSat</sub> = 10mA. (06 Marks)

- 3 a. Define h-parameters and hence derive h-parameter model of a CE-BJT. (06 Marks)

- b. Derive expressions for  $A_i$ ,  $A_v$ ,  $Z_i$  and  $\bar{Z}_0$  for a voltage divider bias circuit of BJT, using approximate hybrid model of BJT. (06 Marks)

- c. A voltage source of negligible internal resistance drives a common collector transistor amplifier. The load resistance is 2500  $\Omega$ . The transistor h-parameters are  $h_{ic} = 1000\Omega$ ,  $h_{rc} = 1$ ,  $h_{fc} = -50$  and  $h_{oc} = 25\mu A/v$ . Compute  $A_i$ ,  $A_v$ ,  $Z_i$  and  $Z_o$ . (08 Marks)

- 4 a. Explain the effect of coupling capacitor and bypass capacitor on the low frequency response of a BJT amplifier. (10 Marks)

- b. Determine the lower cut off frequency for the voltage divider bias BJT amplifier with  $C_S = 10 \mu F$ ,  $C_C = 1 \mu F$ ,  $C_E = 20 \mu F$ ,  $R_S = 1 K \Omega$ ,  $R_1 = 10 K \Omega$ ,  $R_2 = 10 K \Omega$ ,  $R_E = 2 K \Omega$ ,  $R_C = 4 K \Omega$  and  $R_L = 2.2 K \Omega$ ,  $R_C = 100$ ,  $R_C = 20$  and  $R_C = 20$ . (10 Marks)

### PART - B

- 5 a. Derive expressions for Z<sub>i</sub> and A<sub>i</sub> for a Darlington emitter follower circuit. (08 Marks)

- b. A 2 stage cascaded amplifier system is built with stage voltage gains 25 and 40. Both stages have the same bandwidth of 220 kHz with identical lower cutoff frequency of 500 Hz. Find the overall gain bandwidth product. (06 Marks)

- c. Mention the types of feedback connections. For any one type, derive the gain, with feedback and compare it with that without feedback. (06 Marks)

- 6 a. Explain the operation of a transformer coupled class-A amplifier. (08 Marks)

- b. A class-B amplifier using a supply of  $V_{CC} = 30V$  and driving a load of  $16\Omega$ , determine the maximum input power, output power and transistor dissipation. (06 Marks)

- c. Explain the causes of distortion in an amplifier. Also define THD. (06 Marks)

- 7 a. Explain Barkhausen criterion for oscillation. Also give the classification of oscillators.

- (06 Marks)

b. Explain the working of Wien bridge oscillator.

(07 Marks)

c. Explain the working of BJT Colpitt's oscillator.

- (07 Marks)

- 8 a. Derive expression for  $V_{GSQ}$ ,  $I_{DQ}$ ,  $V_{DS}$ ,  $V_S$ ,  $V_G$  and  $V_D$  for a self bias FET circuit. (10 Marks)

- b. Explain the depletion and enhancement type MOSEFTs, their characteristics and frequency response. (10 Marks)

\*\*\*\*